## **SECTION 5 RESETS AND INTERRUPTS**

Resets and interrupt operations load the program counter with a vector that points to a new location from which instructions are to be fetched. A reset immediately stops execution of the current instruction and forces the program counter to a known starting address. Internal registers and control bits are initialized so the MCU can resume executing instructions. An interrupt temporarily suspends normal program execution while an interrupt service routine is being executed. After an interrupt has been serviced, the main program resumes as if there had been no interruption.

#### 5.1 Resets

There are four possible sources of reset. Power-on reset (POR) and external reset share the normal reset vector. The computer operating properly (COP) reset and the clock monitor reset each has its own vector.

#### 5.1.1 Power-On Reset

A positive transition on V<sub>DD</sub> generates a power-on reset (POR), which is used only for power-up conditions. POR cannot be used to detect drops in power supply voltages. A 4064  $t_{cyc}$  (internal clock cycle) delay after the oscillator becomes active allows the clock generator to stabilize. If RESET is at logical zero at the end of 4064  $t_{cyc}$ , the CPU remains in the reset condition until RESET goes to logical one.

It is important to protect the MCU during power transitions. Most M68HC11 systems need an external circuit that holds the  $\overrightarrow{\text{RESET}}$  pin low whenever V<sub>DD</sub> is below the minimum operating level. This external voltage level detector, or other external reset circuits, are the usual source of reset in a system. The POR circuit only initializes internal circuitry during cold starts. Refer to **Figure 2-3**.

#### 5.1.2 External Reset (RESET)

The CPU distinguishes between internal and external reset conditions by sensing whether the reset pin rises to a logic one in less than two E-clock cycles after an internal device releases reset. When a reset condition is sensed, the RESET pin is driven low by an internal device for four E-clock cycles, then released. Two E-clock cycles later it is sampled. If the pin is still held low, the CPU assumes that an external reset has occurred. If the pin is high, it indicates that the reset was initiated internally by either the COP system or the clock monitor. Do not connect an external resistor capacitor (RC) power-up delay circuit to the reset pin of M68HC11 devices because the circuit charge time constant can cause the device to misinterpret the type of reset that occurred.

#### 5.1.3 COP Reset

The MCU includes a COP system to help protect against software failures. When the COP is enabled, the software is responsible for keeping a free-running watchdog timer

from timing out. When the software is no longer being executed in the intended sequence, a system reset is initiated.

The state of the NOCOP bit in the CONFIG register determines whether the COP system is enabled or disabled. To change the enable status of the COP system, change the contents of the CONFIG register and then perform a system reset. In the special test and bootstrap operating modes, the COP system is initially inhibited by the disable resets (DISR) control bit in the TEST1 register. The DISR bit can subsequently be written to zero to enable COP resets.

The COP timer rate control bits CR[1:0] in the OPTION register determine the COP timeout period. The system E clock is divided by 2<sup>15</sup> and then further scaled by a factor shown in **Table 5-1**. After reset, these bits are zero, which selects the fastest timeout period. In normal operating modes, these bits can only be written once within 64 bus cycles after reset.

| CR[1:0] | Divide<br>E/2 <sup>15</sup> By | XTAL = 4.0 MHz<br>Timeout<br>– 0 ms, + 32.8 ms | XTAL = 8.0 MHz<br>Timeout<br>– 0 ms, + 16.4 ms | XTAL = 12.0 MHz<br>Timeout<br>– 0 ms, + 10.9 ms |

|---------|--------------------------------|------------------------------------------------|------------------------------------------------|-------------------------------------------------|

| 0 0     | 1                              | 32.768 ms                                      | 16.384 ms                                      | 10.923 ms                                       |

| 0 1     | 4                              | 131.072 ms                                     | 65.536 ms                                      | 43.691 ms                                       |

| 1 0     | 16                             | 524.28 ms                                      | 262.14 ms                                      | 174.76 ms                                       |

| 11      | 64                             | 2.098 s                                        | 1.049 s                                        | 699.05 ms                                       |

|         | E =                            | 1.0 MHz                                        | 2.0 MHz                                        | 3.0 MHz                                         |

#### Table 5-1 COP Timer Rate Select

#### **COPRST** — Arm/Reset COP Timer Circuitry

Complete the following reset sequence to service the COP timer. Write \$55 to CO-PRST to arm the COP timer clearing mechanism. Then write \$AA to COPRST to clear the COP timer. Performing instructions between these two steps is possible as long as both steps are completed in the correct sequence before the timer times out.

#### 5.1.4 Clock Monitor Reset

The clock monitor circuit is based on an internal RC time delay. If no MCU clock edges are detected within this RC time delay, the clock monitor can optionally generate a system reset. The clock monitor function is enabled or disabled by the CME control bit in the OPTION register. The presence of a timeout is determined by the RC delay, which allows the clock monitor to operate without any MCU clocks.

Clock monitor is used as a backup for the COP system. Because the COP needs a clock to function, it is disabled when the clocks stop. Therefore, the clock monitor system can detect clock failures not detected by the COP system.

**RESETS AND INTERRUPTS**

\$103A

Semiconductor wafer processing causes variations of the RC timeout values between individual devices. An E-clock frequency below 10 kHz is detected as a clock monitor error. An E-clock frequency of 200 kHz or more prevents clock monitor errors. Using the clock monitor function when the E-clock is below 200 kHz is not recommended.

Special considerations are needed when a STOP instruction is executed and the clock monitor is enabled. Because the STOP function causes the clocks to be halted, the clock monitor function generates a reset sequence if it is enabled at the time the STOP mode was initiated. Before executing a STOP instruction, clear the CME bit in the OP-TION register to zero to disable the clock monitor. After recovery from STOP, set the CME bit to logic one to enable the clock monitor. Alternatively, executing a STOP instruction with the CME bit set to logic one can be used as a software initiated reset.

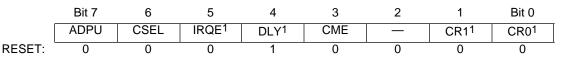

## 5.1.5 Option Register

**OPTION** — System Configuration Options

NOTES:

1. Can be written only once in first 64 cycles out of reset in normal modes, or at any time in special modes.

#### ADPU — Analog-to-Digital Converter Power-Up Refer to **SECTION 10 ANALOG-TO-DIGITAL CONVERTER**.

CSEL — Clock Select

## Refer to SECTION 10 ANALOG-TO-DIGITAL CONVERTER.

- IRQE Configure IRQ for Edge-Sensitive Only Operation

- $0 = \overline{IRQ}$  is configured for level-sensitive operation

- $1 = \overline{IRQ}$  is configured for edge-sensitive only operation

## DLY — Enable Oscillator Startup Delay

# Refer to SECTION 4 OPERATING MODES AND ON-CHIP MEMORY and SECTION 10 ANALOG-TO-DIGITAL CONVERTER.

CME — Clock Monitor Enable

This control bit can be read or written at any time and controls whether or not the internal clock monitor circuit triggers a reset sequence when the system clock is slow or absent. When it is clear, the clock monitor circuit is disabled, and when it is set, the clock monitor circuit is enabled. Reset clears the CME bit.

- 0 = Clock monitor circuit disabled

- 1 = Slow or stopped clocks cause reset

Bit 2 - Not implemented

Always reads zero

\$1039

CR[1:0] - COP Timer Rate Select

The internal E clock is first divided by 2<sup>15</sup> before it enters the COP watchdog system. These control bits determine a scaling factor for the watchdog timer.

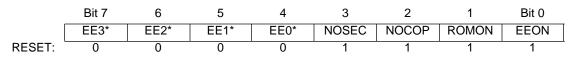

## 5.1.6 CONFIG Register

**CONFIG** — Configuration Control Register

\$103F

#### EE[3:0] — EEPROM Mapping\*

EE[3:0] apply only to MC68HC811E2. Refer to SECTION 4 OPERATING MODES AND ON-CHIP MEMORY.

## NOSEC — Security Mode Disable

Refer to SECTION 4 OPERATING MODES AND ON-CHIP MEMORY.

#### NOCOP — COP System Disable

- 0 = COP enabled (forces reset on timeout)

- 1 = COP disabled (does not force reset on timeout)

#### ROMON — ROM (EPROM) Enable

Refer to SECTION 4 OPERATING MODES AND ON-CHIP MEMORY.

#### EEON — EEPROM Enable

## Refer to SECTION 4 OPERATING MODES AND ON-CHIP MEMORY.

#### 5.2 Effects of Reset

When a reset condition is recognized, the internal registers and control bits are forced to an initial state. Depending on the cause of the reset and the operating mode, the reset vector can be fetched from any of six possible locations. Refer to **Table 5-2**.

| Cause of Reset        | Normal Mode Vector | Special Test or Bootstrap |

|-----------------------|--------------------|---------------------------|

| POR or RESET Pin      | \$FFFE, FFFF       | \$BFFE, \$BFFF            |

| Clock Monitor Failure | \$FFFC, FFFD       | \$BFFC, \$BFFD            |

| COP Watchdog Timeout  | \$FFFA, FFFB       | \$BFFA, \$BFFB            |

#### Table 5-2 Reset Cause, Reset Vector, and Operating Mode

These initial states then control on-chip peripheral systems to force them to known startup states, as follows:

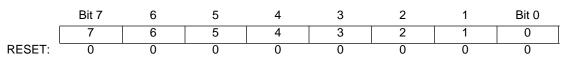

## 5.2.1 Central Processing Unit

After reset, the CPU fetches the restart vector from the appropriate address during the first three cycles, and begins executing instructions. The stack pointer and other CPU

**RESETS AND INTERRUPTS**

registers are indeterminate immediately after reset; however, the X and I interrupt mask bits in the condition code register (CCR) are set to mask any interrupt requests. Also, the S bit in the CCR is set to inhibit the STOP mode.

#### 5.2.2 Memory Map

After reset, the INIT register is initialized to \$01, mapping the RAM at \$00, and the control registers at \$1000. For the MC68HC811E2, the CONFIG register resets to \$FF. EEPROM mapping bits (EE[3:0]) place the EEPROM at \$F800. Refer to the memory map diagram for MC68HC811E2 in **SECTION 4 OPERATING MODES AND ON-CHIP MEMORY**.

#### 5.2.3 Timer

During reset, the timer system is initialized to a count of \$0000. The prescaler bits are cleared, and all output compare registers are initialized to \$FFFF. All input capture registers are indeterminate after reset. The output compare 1 mask (OC1M) register is cleared so that successful OC1 compares do not affect any I/O pins. The other four output compares are configured so that they do not affect any I/O pins on successful compares. All input capture edge-detector circuits are configured for capture disabled operation. The timer overflow interrupt flag and all eight timer function interrupt flags are cleared. All nine timer interrupts are disabled because their mask bits have been cleared.

The I4/O5 bit in the PACTL register is cleared to configure the I4/O5 function as OC5; however, the OM5:OL5 control bits in the TCTL1 register are clear so OC5 does not control the PA3 pin.

#### 5.2.4 Real-Time Interrupt (RTI)

The real-time interrupt flag (RTIF) is cleared and automatic hardware interrupts are masked. The rate control bits are cleared after reset and can be initialized by software before the real-time interrupt (RTI) system is used.

#### 5.2.5 Pulse Accumulator

The pulse accumulator system is disabled at reset so that the pulse accumulator input (PAI) pin defaults to being a general-purpose input pin.

#### 5.2.6 Computer Operating Properly (COP)

The COP watchdog system is enabled if the NOCOP control bit in the CONFIG register is cleared, and disabled if NOCOP is set. The COP rate is set for the shortest duration timeout.

## 5.2.7 Serial Communications Interface (SCI)

The reset condition of the SCI system is independent of the operating mode. At reset, the SCI baud rate control register (BAUD) is initialized to \$04. All transmit and receive interrupts are masked and both the transmitter and receiver are disabled so the port pins default to being general-purpose I/O lines. The SCI frame format is initialized to

an 8-bit character size. The send break and receiver wakeup functions are disabled. The TDRE and TC status bits in the SCI status register (SCSR) are both ones, indicating that there is no transmit data in either the transmit data register or the transmit serial shift register. The RDRF, IDLE, OR, NF, FE, PF, and RAF receive-related status bits in the SCI control register 2 (SCCR2) are cleared.

### 5.2.8 Serial Peripheral Interface (SPI)

The SPI system is disabled by reset. The port pins associated with this function default to being general-purpose I/O lines.

#### 5.2.9 Analog-to-Digital Converter

The A/D converter configuration is indeterminate after reset. The ADPU bit is cleared by reset, which disables the A/D system. The conversion complete flag is indeterminate.

#### 5.2.10 System

The EEPROM programming controls are disabled, so the memory system is configured for normal read operation. PSEL[3:0] are initialized with the value %0110, causing the external IRQ pin to have the highest I-bit interrupt priority. The IRQ pin is configured for level-sensitive operation (for wired-OR systems). The RBOOT, SMOD, and MDA bits in the HPRIO register reflect the status of the MODB and MODA inputs at the rising edge of reset. MODA and MODB inputs select one of the four operating modes. After reset, writing SMOD and MDA in special modes causes the MCU to change operating modes. Refer to the description of HPRIO register in **SECTION 4 OPERATING MODES AND ON-CHIP MEMORY** for a detailed description of SMOD and MDA. The DLY control bit is set to specify that an oscillator start-up delay is imposed upon recovery from STOP mode. The clock monitor system is disabled because CME is cleared.

#### 5.3 Reset and Interrupt Priority

Resets and interrupts have a hardware priority that determines which reset or interrupt is serviced first when simultaneous requests occur. Any maskable interrupt can be given priority over other maskable interrupts.

The first six interrupt sources are not maskable. The priority arrangement for these sources is as follows:

- 1. POR or RESET pin

- 2. Clock monitor reset

- 3. COP watchdog reset

- 4. XIRQ interrupt

- 5. Illegal opcode interrupt

- 6. Software interrupt (SWI)